# **Stratos and Morello?**

Joakim Bech - 2020-12-15

10011 00100000 01110100 011011

0111 01101000 01100

1100101 01110010 011

01110101 01110010

10 01111001

100 01101100 01111001

0101 01110101 01110010 011.

01101110 01101101

1

## Capability based security systems

#### <u>What it is</u>

- Capabilities are unforgeable tokens

- Access to resources goes via capabilities

#### <u>ldea is to</u>

- limit the damage when software misbehaves

- Implement principle of least privilege

- l.e., use no more privileges than needed

- Implement principle of intentional use

- I.e., the answer to the "<u>confused deputy</u>" problems. Avoid trick a more privileged program into misusing its authority

- Formally verify the system

#### Existing software

There are software implementations / variants of this, <u>Capsicum</u> (FreeBSD), <u>Linux capabilities</u>, seccomp etc.

## CHERI

#### What is it?

- A project that has been running for roughly 10 years already ...

- Architectural protection model

- Leverage hardware to implement a capability based system

- ISA extended to include security primitives

#### <u>Idea is to</u>

- Mix software and hardware to come up with a capability based system that is more robust to well known attacks, as for example

- Buffer overflows

- Return oriented programming (ROP)

- And many other known vulnerability classes ...

- Implement compartmentalization (high granularity)

- Use hardware to get the needed performance and atomicity

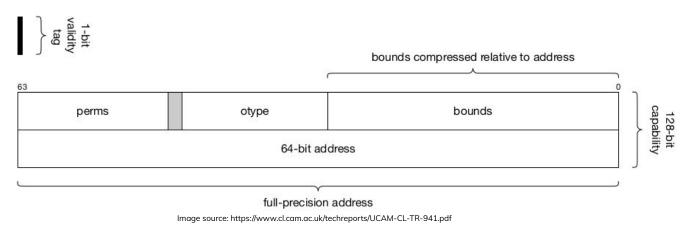

#### CHERI #2 - 128-bit capability

- A capability in CHERI embeds

- Permission bits (perms)

- Can be used to "seal" capabilities (otype)

- Bounds that pointers can operate on (bounds)

- A traditional pointer (at the last half of the capability)

- A tag bit telling whether the capability is trustworthy or not

### CHERI #3 - compilation modes

#### Pure-capability code

- Implements all C/C++ pointer types, as well as all implied pointers (e.g., return addresses, the stack pointer, and so on) using capabilities.

- ABI disruptive change

#### Hybrid-capability code

- Implements pointer types using integers by default, interpreted with respect to a global default data capability (DDC) able to address code, globals, heap, and stack(s).

### CHERI #4 - Software

#### How does software deal with this?

- Toolchains: Involves lots of changes to LLVM, LLDB, GCC, GDB etc

- In short all software must go through a "CHERIfication" to be able to leverage all this

- Add / user compiler intrinsics

- Change pointers to capabilities

- Adapt syscall layers

- Do pure- or hybrid-capability implementations

## DSbD - Digital Security by Design

- It's a (UK) government funded project headed by UK Research and Innovation (UKRI)

- Quote from the UKRI DSbD page: \_

"The ISCF Digital Security by Design challenge aims to radically update the foundation of the UK's insecure digital computing infrastructure. The challenge will:

01 01110010

01110 01101101

01101 01100001 01.

100100 00100000 01100101 011

00100000 01110100 01101111 0

00100000 01110100 01101111 0010000

01100101 01110010 01100001

1 01101000 01100101 01110

100 01101111 011001

- Increase cyber security for businesses, government and the wider public and economy;

- Increase productivity to the UK through reduction of days lost to cyber-attacks;

- Make the UK market-leader through new capabilities fostering the trust that is necessary for successful adoption of future digital services in areas such as artificial intelligence (AI) and the Internet of things (IoT)."

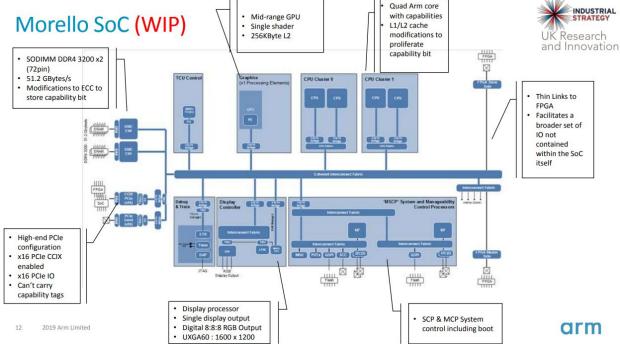

### The Arm Morello project

- On a high level: Implement and run CHERI on Armv8-A

- Focuses on Linux kernel and user space (Android "nano" environment)

- Think framework enablement and commonly used tools

- Python, Ruby, Go, QT ...

- I.e., to be able to attract other people than researchers, it must be possible to engineers to convert and run their scripts, binaries etc without too much work

01 01110010

00100000 01110100 01101111 0010007

- Firmware, boot loaders and secure side (TrustZone) is low priority for the moment in the Morello project

### The Arm Morello board

- Prototype board based on Arm <u>Neoverse N1</u>

- Released to partners somewhere in Q3 2021

- Virtual platforms Arm Morello FVP will be used until hardware exists

- Morello FVP will be released to the public in October 2020

### The Arm Morello board

TOLLED DILLOW

101110 01100100 01110101 01100011

10 01111001 00100000

00101 01100100 00100000 01100101 0110

110111 01101000 01100101 01110010 0110

01100101 01110010 01100001 01110100 0111

11110110 01100101 01110010 01101000 01100

1101101 00100000 01110100 01101111 de 10010 01110011 00100000 01110111 011 111 01101110 01100100 01110101 01100011 d

11 01101110 00100000 01110100 01101000

01100101 01100100 00100000 01100101 011

01110111 01101000 01100101 01110010 0111

01101 01100001 01101110 01111001 0010000

9100 00100000 01101111 01100110 0110011

000000000

10 01110100 01101111 00100000 0114

Inaro

00100000 01110100 01101111 00100000

01 01110010

01110 01101101

01111001

1110 01101101

01110010 01110011 00100000

01100100 00100000 01101111

01

Image source: https://www.cl.cam.ac.uk/research/security/ctsrd/cheri/cheri-morello.html

### Food for thought - Stratos on Morello?

Motivation?

- Morello focus is on the non-secure side

- It's about framework enablement

- Many of the deliverables for Stratos is about framework improvements on the non-secure side (i.e., a plain Linux environment)

- Seems like making Stratos ready for Morello could be worthwhile

- Combine Morello project goals with areas of interest to Linaro members

- In short: Hardening hypervisors

#### Challenges and risks?

- "CHERIfication" is a bit invasive, so it won't be easy to share code base

- The Morello project is a research/prototype project, i.e., no guarantees that it'll be successful

- Morello hardware can be a challenge

#### Resources

- University of Cambridge

- Main page:

http://cheri-cpu.org

- Morello page:

https://www.cl.cam.ac.uk/research/security/ctsrd/cheri/cheri-morello.html

- UKRI

- Digital Security by Design

https://www.ukri.org/innovation/industrial-strategy-challenge-fund/digital-security-by-design

- Arm

- Arm Morello program

https://developer.arm.com/architectures/cpu-architecture/a-profile/morello

Morello Architecture specification (pdf)

https://documentation-service.arm.com/static/5f7460641b758617cd95ab98

- Neoverse N1

https://developer.arm.com/ip-products/processors/neoverse/neoverse-n1

# Thank you

An (m100101

110 01111001

11

101 01110101 01110010

10011 00100000 01110100 0110111

110111 01101000 011001