## **QEMU** Overview

Edgar E. Iglesias Principal Software Engineer April/19/2022

- QEMU Overview

- Co-simulation / Hybrid

- Plans

- Demos

## **QEMU Overview**

#### Virtual Platform for SW developers

| <ul> <li>Open-Source</li> <li>@Xilinx from 2009</li> <li>Transaction level</li> <li>Debug &amp; Profiling</li> <li>Co-simulation</li> <li>Value</li> </ul> | Scalable distribution & cost model, Popular in Open-Source community<br>MicroBlaze, Power PC, ARM (Zynq, Zynq MPSoC, Versal), x86<br>Fast but not cycle accurate, Linux boot 2sec to user-space, 2min to prompt<br>GDB/XSDB, traces, code-coverage and error-injection (-ve testing)<br>SystemC/TLM-2, RTL and Hybrid<br>Shift left (early SW development), Cost, Speed and Flexibility |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jsers                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul><li>Internal</li><li>External</li></ul>                                                                                                                | BootROM, System Software, SVT<br>Petalinux, Vitis HW-Emulation, GitHub (Roll your own)                                                                                                                                                                                                                                                                                                  |

| Success stories                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul><li>Zynq MPSoC</li><li>DARPA/POSH</li><li>Customers/Vendors</li></ul>                                                                                  | Xilinx a significant contributor to ARMv8, MicroBlaze, RegAPI, Reset, Clocks etc<br>Xilinx chosen for Open-Source QEMU Co-simulation efforts<br>X (PetaLinux), Y (Github) and Z (Vitis)                                                                                                                                                                                                 |

EMU

### **QEMU** modes

#### System Emulation

- Emulation of full system (TCG)

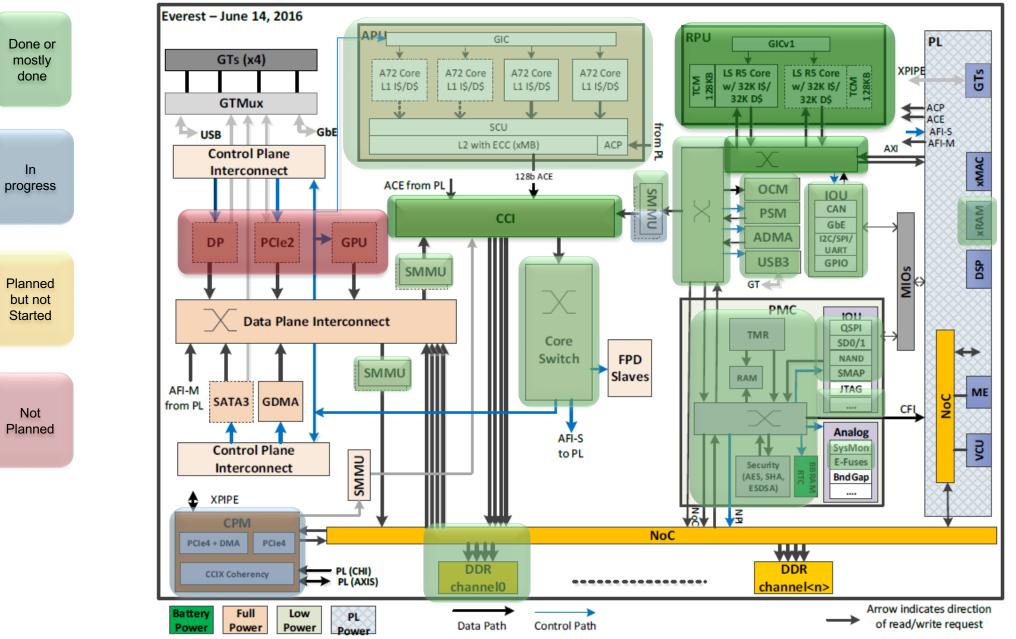

- Including Virtualization & Security, heterogenous cores, TZ, IOMMU's, XMPU's, PMU, PMC etc

- DTB machines

#### Hypervisor KVM

- HW accelerated virtualization

- ZU+, Generic ARM virtual board

- x86 + PCIe co-simulation

#### Linux-user

- Cross-run Linux binaries (e.g ARM Linux binary on x86 Linux host)

- GCC test-suite, Cross-compilation, Rootfs testing

**E** XILINX.

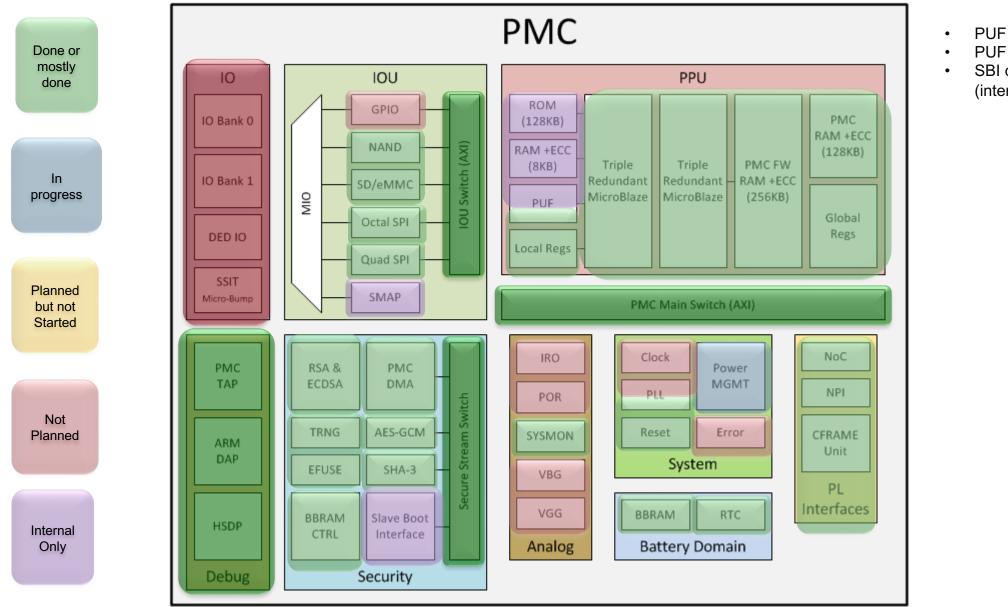

- PUF Firmware model public

- SBI depends on BootROM (internal-only)

**E** XILINX.

## **QEMU System Emulation**

## Boot

- Full boot through BootROM (internal only)

- FSBL, U-boot & Linux direct boots

## Security

- CSU, PMC-Secure, crypto blocks, EL3/TZ

- Secure-boot depends on BootROM images (internal)

## **QEMU System Emulation**

### Debuggers

- GDB

- XSDB (PetaLinux, Vitis and Vivado)

#### Testing

- QTX Pytest based test-suite 500 cases

- TBM Baremetal test and exploration environment

- PetaLinux 500+ testcases, Vitis 500+ co-simulation test-cases

#### Tools

- Etrace tracing and code coverage

- Xregdb, irqmap-gen, memmap-gen Machine and model skeleton/generation

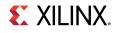

## **Co-simulation / Hybrid**

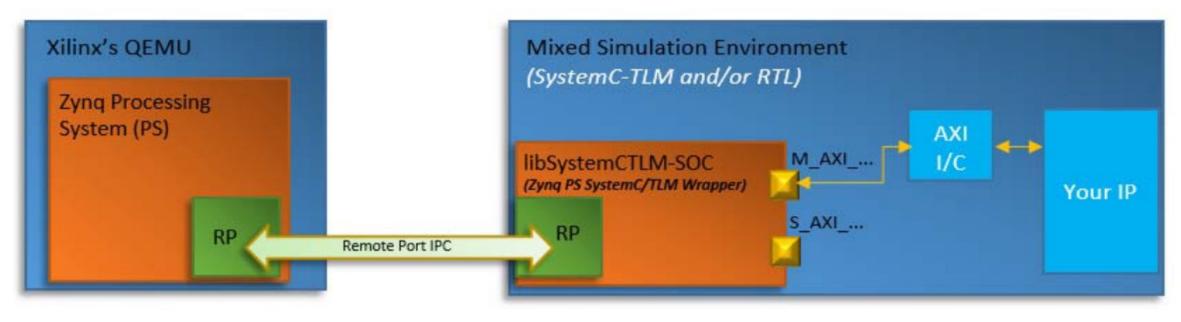

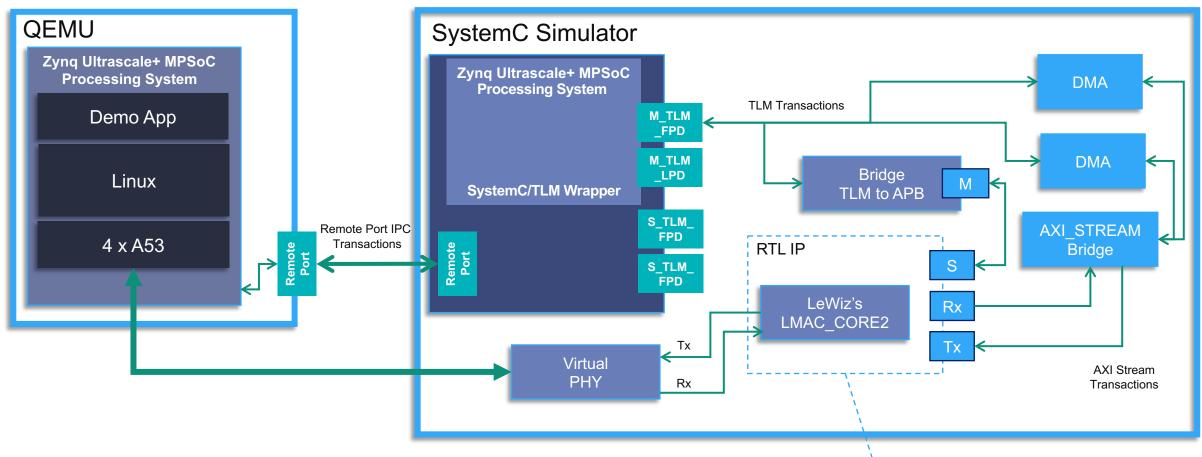

#### **Open Source Mixed Simulation Environment**

LibSystemCTLM-SoC

https://github.com/Xilinx/libsystemctlm-soc

Based on Open-Source Projects

Phase 1a

Phase 1b

## Xilinx Vivado/Vitis Co-sim

Unique Process

Xilinx's Remote Port

Xilinx's Zynq PS or PS SystemC/TLM Wrapper

Zynq PS – PL AXI Master/Slave Ports

Your IP(s)

## **TLM2 bridges RTL simulation**

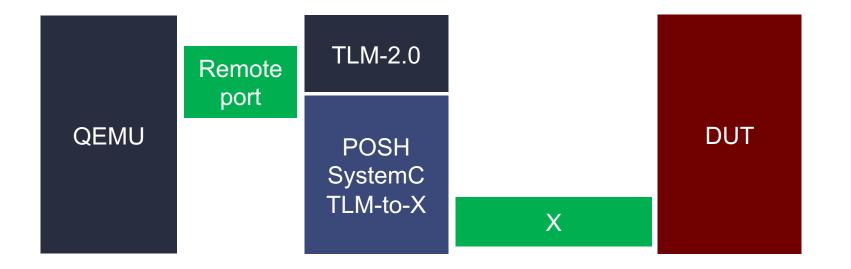

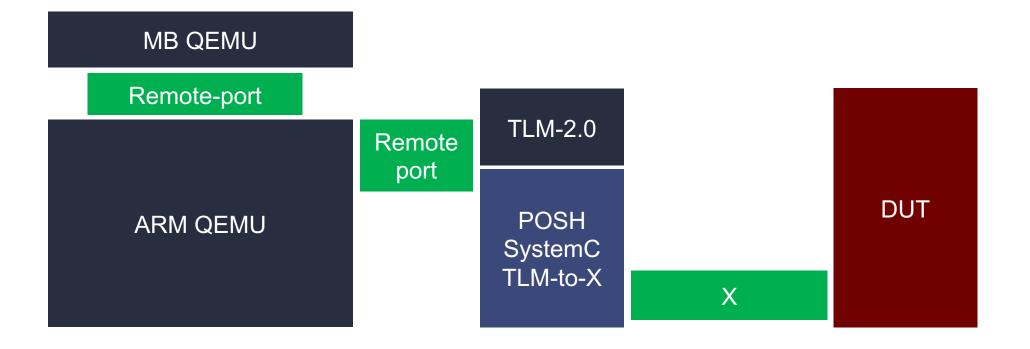

### **QEMU** heterogeneous

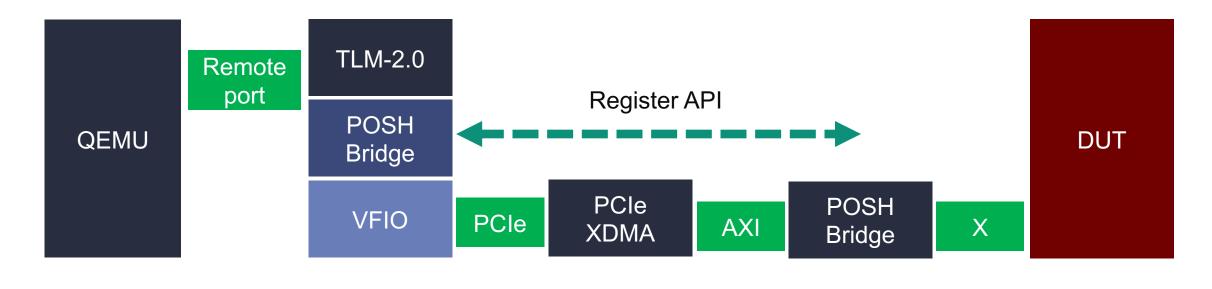

## **TLM2 bridges FPGA Prototyping**

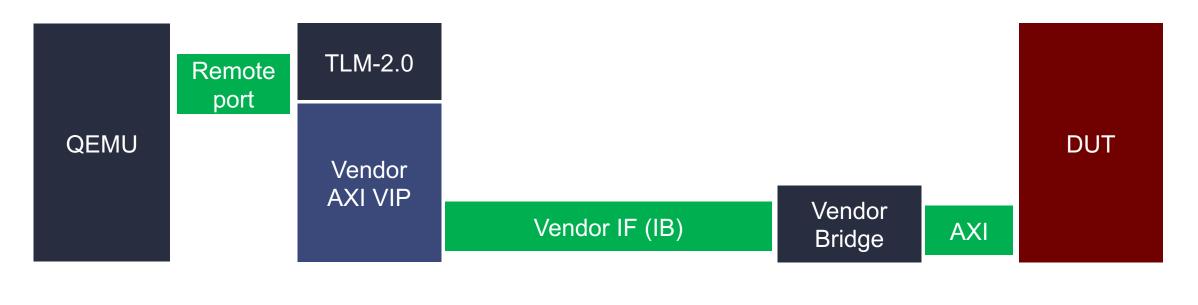

## **TLM2 bridges Emulator (Initial idea)**

Pros: Fast, sort of "Vendor neutral" Cons: Not debug-portable, Licensing AXI VIP

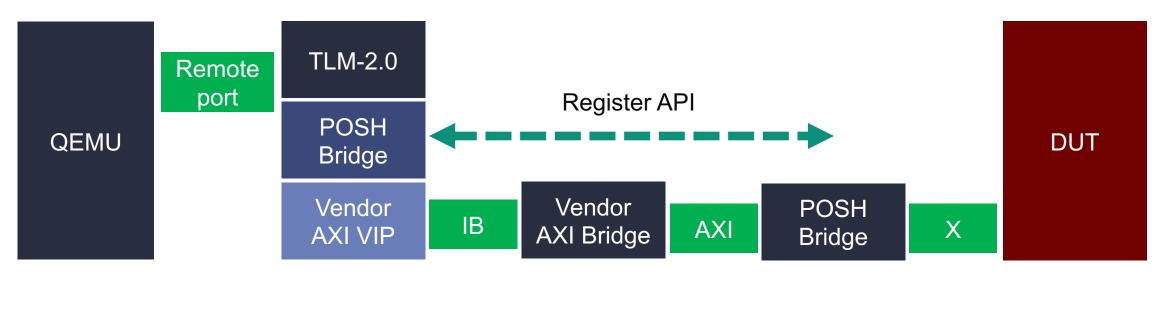

### **TLM2 bridges Emulator**

Pros: Vendor neutral, debug-portable Cons: Slow, Licensing AXI VIP

## Plans around QEMU upstream

| Upstream | Heterogenous<br>CPUs<br>Done | Heterogenous<br>CPUs<br>Needed |

|----------|------------------------------|--------------------------------|

|          |                              |                                |

| CPUs                     | MicroBlaze                                                    | ARMv8 (EL2,<br>EL3)                                                        | PPC 440<br>BookE                                   | MIPS (R32<br>SMP, SMT),<br>CRIS                         | MTTCG,<br>Per CPU AS                                               | CPU Clusters,<br>GDB Multi-<br>process      | Heterogenous<br>CPU build and<br>instance<br>support<br>(submitted) |

|--------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------|

| Interrupt<br>controllers | Xilinx Intc                                                   | GICv2 (Virt),<br>ZynqMP IPI                                                | PPC XInx Intc                                      | EtraxFS PIC                                             |                                                                    | Multiple GICs                               |                                                                     |

| Peripherals              | Xilinx UARTs,<br>Cadence UART,<br>DMA, Display                | SPI, QSPI,<br>Octal SPI,<br>m25p80, NAND                                   | SDHCI, eMMC,<br>AHCI Sysbus                        | USB Sysbus,<br>ZynqMP, Versal                           | Ethernet<br>(MACb, Ethlite,<br>AXI eth),<br>EtraxFS,<br>MDIO, PHYs | PMU, PMC.<br>PSM devices                    |                                                                     |

| Frameworks               | Register API                                                  | Clock API                                                                  | Reset API                                          | Named<br>GPIOs/Interrup<br>ts                           | Streaming API                                                      | Generic CPU<br>reset & halt<br>(GPIO based) |                                                                     |

| Machines                 | Zynq, ZynqMP,<br>Versal,<br>PetaLinux MB,<br>Virtex ML507 etc | Versal<br>Cortex-A72 +<br>Cortex-R5F<br>CRL (Dynamic<br>wake-up of<br>RPU) | QMP driven<br>machines<br>(ongoing),<br>DTB driven | ZynqMP, Versal<br>Cortex-R5F<br>GIC,<br>IPI connections | PMU, PMC,<br>PSM<br>subsystems                                     |                                             |                                                                     |

### Programs

Pre tape-out

Post tape-out

| Pre-RTL                                                                                                                                                      | RTL Emnulation and FPGA<br>Prototyping                                                                                                                                          | Internal/Not public                                                             | Public                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QEMU is the only platform<br>SSW Bring-up<br>BootROM development<br>Arch exploration<br>Prep for Emu and Proto<br>Boot Firmware, TF-A, U-boot,<br>Xen, Linux | Migration towards RTL<br>QEMU still used due to<br>productivity gains (turnaround<br>speed) and due to RTL<br>development lag<br>CI loops SW/HW/QEMU<br>More complex SSW setups | Prep for VnC<br>Integrate into PetaLinux, Vitis, Vivado<br>Prep for upstreaming | Open-Source community<br>Early-Access programs<br>Customer support<br>Plans 2022.2:<br>QEMU upstream:<br>Versal eMMC<br>Versal SSS and SHA<br>Versal CAN-FD<br>M25p80 Octal SPI offchip dev<br>ZynqMP Display-Port fixes<br>ZynqMP USB minor alignments<br>ZCU102 i2c clock-devs<br>ZCU102 DDR SODIMM SPD<br>QMP machines (GreenSocs)<br>LibsystemctIm-soc:<br>PCIe core (TLP level) TLM<br>Versal PCIe end-point model<br>including PS/PMC |

## Demo

**E** XILINX.

## **DARPA/POSH**

#### Main Lessons Learnt

- Need Backend connections to the RTL/TLM to feed in real data

- Need for AXI Stream and APB Protocols

- Need to standardize on a particular set of protocols....AXI, Wishbone?

- Successfully identified bug in IP RTL during integration !

LeWiz Communications Ethernet MAC Core2 10G/5G/2.5G/1G

https://github.com/lewiz-support/LMAC\_CORE2

## **XILINX**

# **Thank You**